Data Sheet

ADP5042

Rev. A | Page 27 of 32

EVALUATION BOARD SCHEMATICS AND ARTWORK

SW

VOUT1

PGND

MODE

C6

10礔

L1

1礖

VIN1

TP1

TP2

TP11

TP6

TP5

TP8

EN3

EN1

VIN2

VIN3

EN2

AGND

C2

1礔

VOUT2

VOUT3

WSTAT

WDI1

WDI2

nRSTO

TP12

C4

1礔

C5

4.7礔

IN1 = 2.3V

TO 5.5V

AVIN

R

FILT

30&

AVIN

VIN2 = 1.7V

TO 5.5V

C1

1礔

VIN3 = 1.7V

TO 5.5V

C3

1礔

VOUT1 AT

800mA

VOUT2 AT

300mA

VOUT3 AT

300mA

TP4

TP9

TP10

TP7

TP3

EN_BK

BUCK

EN_LDO1

LDO1

EN_LDO2

LDO2

AVIN

Figure 67. Evaluation Board Schematic

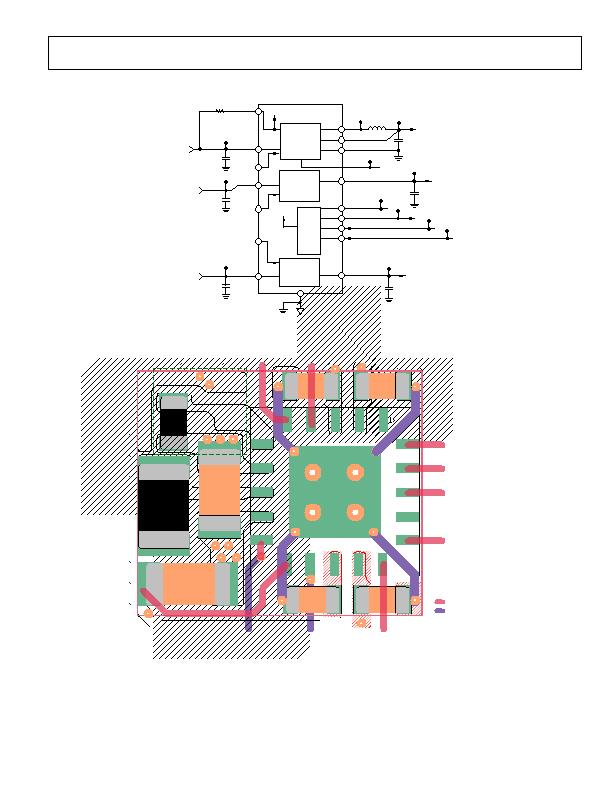

SUGGESTED LAYOUT

0.5

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

1.0

1.5

2.0

2.5

3.0

3.5

VIAs LEGEND

mm

mm

6.0

6.5

MODE

VIN1

SW

PGND

EN1

4.0

4.5

5.0

5.5

6.0

C6 - 10?/SPAN>F

6.3V/XR5 0603

GPL

1.5V

3.3V

7.0

TOP LAYER

SECOND LAYER

PPL

C4 1礔

6.3V/XR5

0402

C1 1礔

10V/XR5

0402

C2 1礔

10V/XR5

0402

PPL = POWER PLANE (+4V)

GPL = GROUND PLANE

1.8V

AGND

ADP5042

GPL

GPL

GPL

GPL

PIN 1

EN2

NC

WDI1

WMOD

MR

C3 1礔

6.3V/XR5

0402

GPL

GPL

GPL

GPL

GPL

PPL

PPL

PPL

Figure 68. Layout

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADT6402SRJZ-RL7

IC TEMP SENS TRIP PT PP SOT-23-6

ADT6501SRJZP085RL7

IC TEMP SENSOR MICROPWR SOT23-5

ADT7302ARTZ-500RL7

IC SENSOR TEMP 13BIT DGT SOT23-6

ADT7310TRZ

IC TEMP SENSOR 16BIT SPI 8SOIC

ADT7461AARMZ-R

IC TEMP SENSOR DGTL 2CH 8-MSOP

ADT7461ARMZ-2R

IC TEMP SENSOR DGTL 2CH 8-MSOP

ADT7463ARQZ-REEL

IC REMOTE THERMAL CTRLR 24-QSOP

ADT7476AARQZ-R

IC REMOTE THERMAL CTLR 24QSOP

相关代理商/技术参数

ADP5042CP-1-EVALZ

功能描述:电源管理IC开发工具 Output Buck Regulator + Dual Fixed Eval RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V

ADP5042CP-2-EVALZ

功能描述:电源管理IC开发工具 Output Buck Regulator + Dual Fixed Eval RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V

ADP5043ACPZ-1-R7

功能描述:IC REG DL BUCK/LINEAR 20LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 线性 + 切换式 系列:- 标准包装:2,500 系列:- 拓扑:降压(降压)同步(3),线性(LDO)(2) 功能:任何功能 输出数:5 频率 - 开关:300kHz 电压/电流 - 输出 1:控制器 电压/电流 - 输出 2:控制器 电压/电流 - 输出 3:控制器 带 LED 驱动器:无 带监控器:无 带序列发生器:是 电源电压:5.6 V ~ 24 V 工作温度:-40°C ~ 85°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*

ADP5043CP-1-EVALZ

功能描述:BOARD EVAL ADP5043CP-1 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969

ADP50450003CBZR

制造商:Analog Devices 功能描述:

ADP50460008CBZR

制造商:Analog Devices 功能描述:

ADP5050

制造商:AD 制造商全称:Analog Devices 功能描述:5-Channel Integrated Power Solution with Quad Buck Regulators and 200 mA LDO Regulator

ADP5050ACPZ-R7

功能描述:PMIC 解决方案 Adj 12V uPMU 4Buck+LDO+I2C I/F

RoHS:否 制造商:IDT 安装风格: 封装 / 箱体: 封装: